Physical Design 이란?

Physical Design에 대해 알아보기

Physical Design 이란?

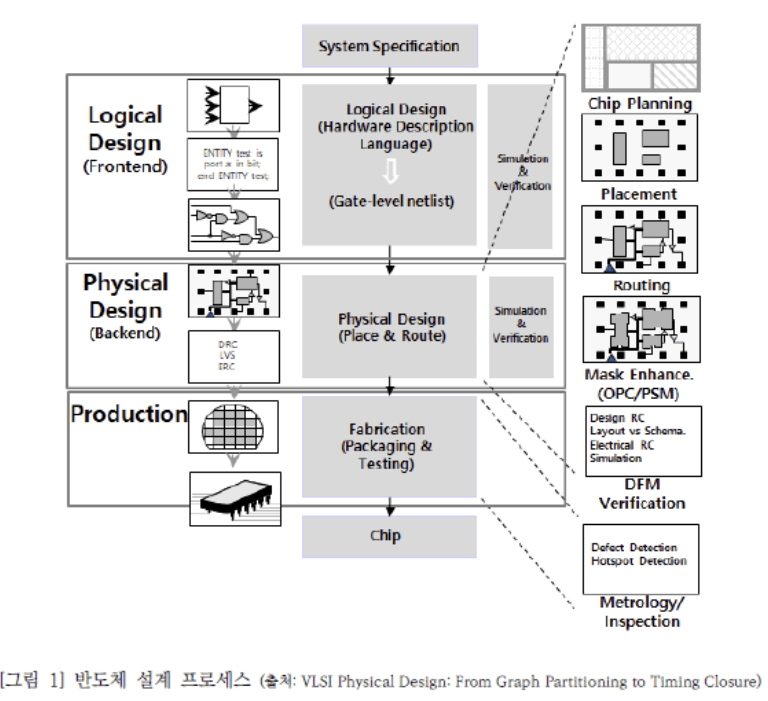

Physical Design은 반도체 칩 설계 과정에서 논리적으로 구현된 회로를 실제 Wafer상에 구현하기 위해 물리적인 칩의 형태로 변환하는 과정입니다.

일반적으로 반도체 칩 설계는 크게 두 단계로, RTL(Register Transfer Level) 설계 및 Logic Synthesis를 통해 Gate-level Netlist를 생성하는 Front-end Design과 Physical Design을 통해 Layout을 생성하는 Back-end Design으로 나뉘어 진행됩니다.

즉, Physical Design은 Gate-level Netlist로 구현된 논리 회로를 공정을 통해 제조 가능한 물리적인 회로(Physical Layout)로 변환하는 작업이라고 할 수 있으며 보통 아래와 같은 순서로 진행됩니다.

1) Partitioning & Floorplanning

반도체 칩 내부의 큰 블록들(Macro, Standard Cell, IP 등)의 배치를 결정합니다.

전력 공급망(Power Plannning) 설계도 이 단계에서 진행되며 PPA(Power, Performance, Area)를 최적화하기 위한 초기 단계입니다.

2) Placement (배치)

논리적 설계 단계에서 생성된 게이트들(Logic Cells, Standard Cells)을 특정 위치에 배치합니다.

배선이 원활하게 이루어질 수 있도록 고려하면서 최적의 위치를 찾습니다.

3) Clock Tree Synthesis (CTS, 클럭 트리 합성)

칩 전체에 걸쳐 클럭 신호를 균등하게 전달하기 위한 클럭 트리를 설계합니다.

4) Routing (배선)

배치된 셀들을 서로 연결하는 배선을 실제 레이어(Layer) 상에 배치하는 과정입니다.

5) Physical Verification (물리적 검증)

Design Rule Check (DRC): 반도체 공정에서 요구하는 디자인 규칙을 만족하는지 검사합니다.

Layout vs. Schematic (LVS): 실제 배선(Layout)과 논리 회로(Schematic)가 일치하는지 검증합니다.

Parasitic Extraction (PEX): 배선에 의한 기생 저항/커패시턴스를 추출하여 성능을 분석합니다.

Static Timing Analysis(STA): 반도체 회로에서 신호의 전파 지연을 분석하여 타이밍이 정상적으로 동작하는지 검증합니다.

이와 같은 Physical Design은 성능, 전력, 면적을 최적화 하면서 제조 가능성[DFM 이란?]을 고려해야 하는 아주 복잡한 과정으로, 이를 위해 고급 EDA 툴과 다양한 최적화 기법이 사용됩니다.

Layout으로 변환된 설계도는 GDS 또는 OASIS 형식의 파일로 저장이 되며, 최종 검증(Signoff) 후 해당 설계도를 Foundry 회사에 전달하는 과정을 MTO(Mask Tape-Out)라고 지칭합니다. MTO가 완료된 Layout 설계도는 MDP 과정을 통해 Photomask로 제작되어 반도체 칩 제조를 위해 사용됩니다.[MDP 란?]

-참고 Article